飞凌连载-NXP iMX8MQ设计底板硬件指南

飞凌连载-NXP iMX8MQ设计底板硬件指南本文以飞凌嵌入式OKMX8MQ-C开发板为基础讲解,其它iMX8MQ品牌产品请参考使用,本文旨在为依托飞凌FETMX8MQ-C核心板自

本文以飞凌嵌入式OKMX8MQ-C开发板为基础讲解,其它iMX8MQ品牌产品请参考使用,本文旨在为依托飞凌FETMX8MQ-C核心板自行设计底板的用户提供设计指导,提示在iMX8MQ产品设计过程中的注意事项,辅助理解设计要点,帮助规避可能遇到的问题。 本期主要介绍9-15节,详情请参照iMX8MQ设计指南。

iMX8MQ 设计指南:

1、核心板电源

2、底板电源

3、BOOT启动部分电路

4、SYS_nRST和ONOFF按键

5、调试串口

6、TF卡电路

7、OTG电路

8、USB_HUB电路

9、千兆网电路

10、HDMI部分电路

11、PCIE部分电路

12、4G部分电路

13、MIPI_DSI/CS

14、SPI转CAN部分电路

15、没有用到的引脚处理方式

注:本文介绍核心板为FETMX8MQ-C核心板;底板为 OKMX8MQ开发板(采用底板+核心板 分离结构)中的底板。

_ueditor_page_break_tag_接上篇:https://www.forlinx.com/article-new-c22/609.html

正文开始:

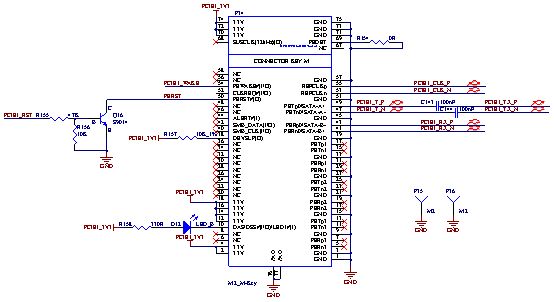

9、千兆网电路

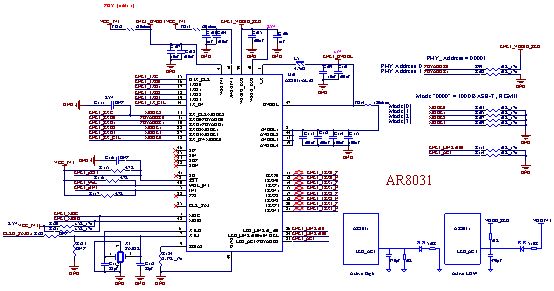

i.MX8MQ核心板上信号线做了分组等长,等长规则为25mil。客户自行设计底板时请注意以下事项:

1、 R124必须选择2.37K_1%的精密电阻,靠近PHY芯片放置;

2、 ENET_MDIO需加1.5K上拉电阻,ENET_MDC可以不加;

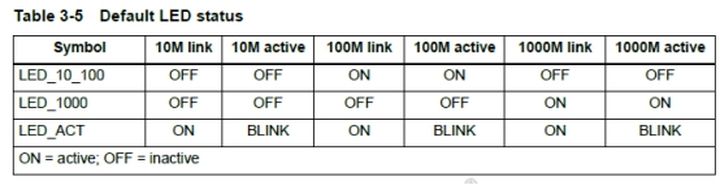

3、 PHYADDR0、PHYADDR1为AR8031 PHY地址配置引脚,为了不修改软件,建议直接参考开发板;MODE0、MODE1、MODE2、MODE3为PHY芯片模式选择,建议参考iMX8MQ 开发板。LED部分配置请参考AR8031手册3.7 LED interface章节,下图为默认状态:

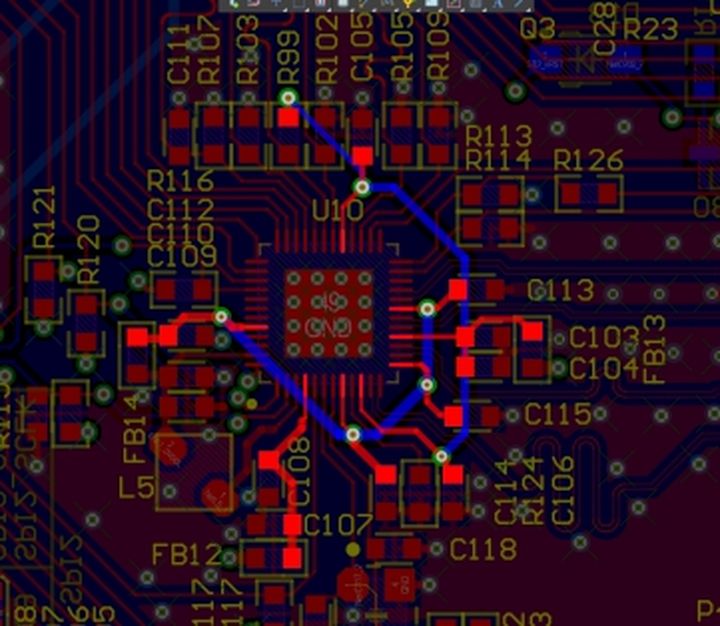

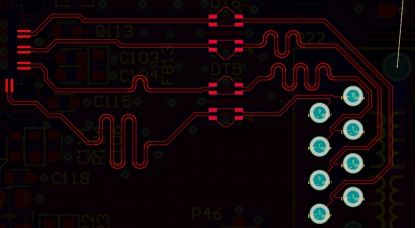

4、 滤波和退耦电容C107、C108、C103、C104、C105、C106、C113、C112、C114、C115需靠近PHY芯片放置,如下图所示:

5、 VDD3V3、AVDD3V3、AVDDL需加磁珠进行隔离,电源走线尽量加粗,请参考开发板设计。

6、 核心板RGMII接口IO电平为2.5V,因此AR8031芯片的29引脚VDDIO_REG和10引脚VDDH_REG需要短接,以将AR8031的IO电平配置为2.5V。

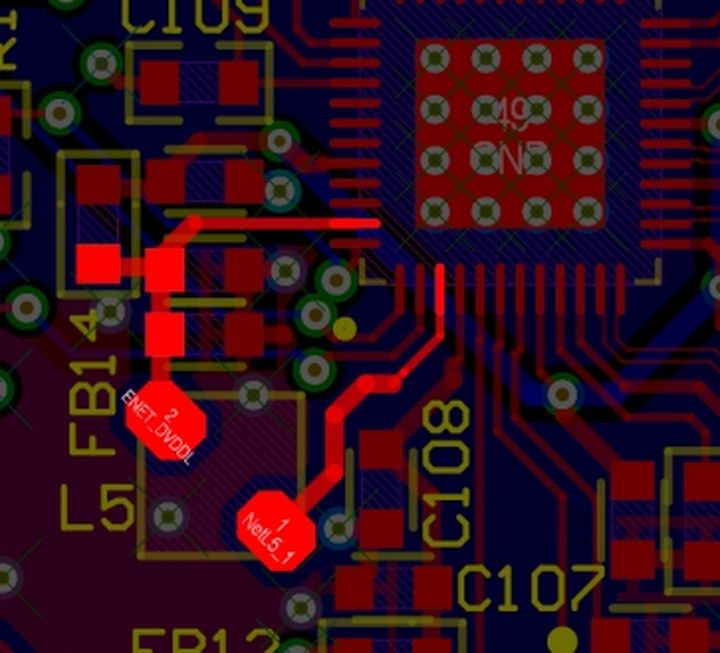

7、 电感L5靠近PHY芯片摆放,C109、110靠近L5摆放。如下图所示:

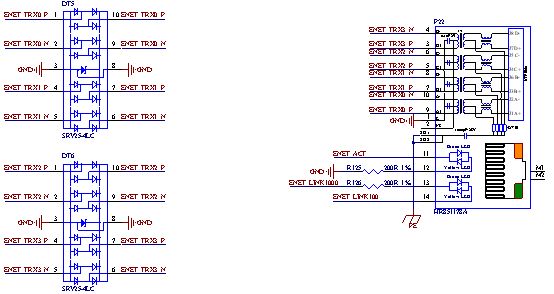

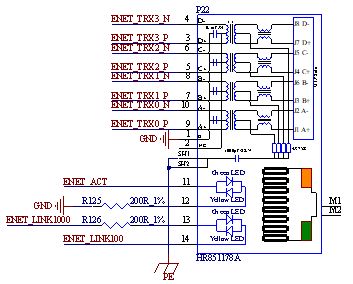

8、 网络变压器的中心抽头需接电容到GND,开发板使用的是内置网络变压器的网口座,内部集成了100nF电容,如果用户使用外置网络变压器,则需自己加上100nF电容。如下图所示:

9、 差分传输线上的ESD需使用低电容器件,否则会导致千兆通讯不稳定。

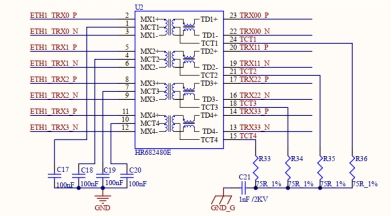

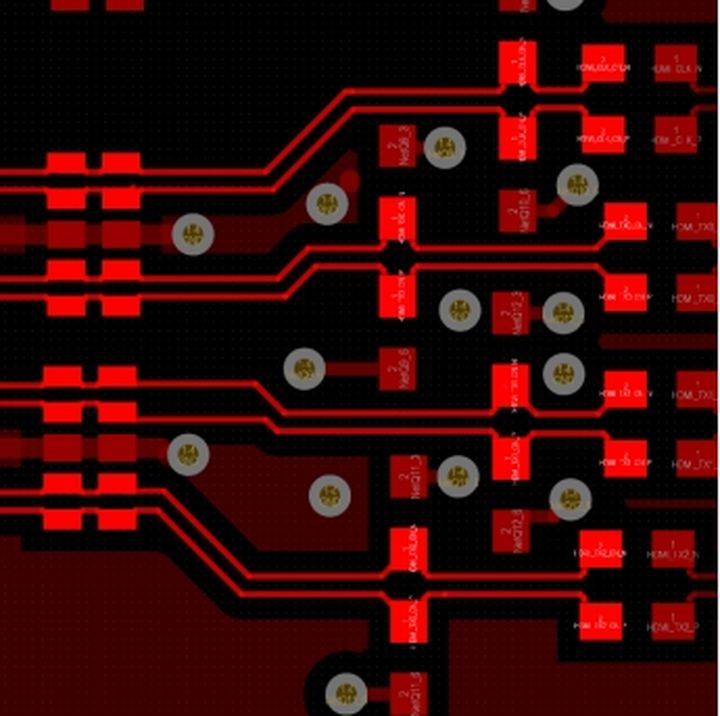

10、PHY芯片尽量靠近网口座摆放,以缩短差分链路走线;四对差分线建议做等长处理,等长要求≤1000mil,阻抗控制为100ΩDifferential ±10%,如下图所示:

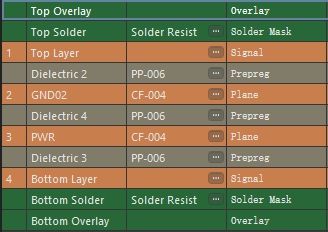

11、PCB层叠参考开发板设计,采用4层板,表层走线,走线相邻层内层为参考GND,剩余内层为VCC。如下图所示:

12、该部分原理图及PCB建议直接复制开发板,如需改动,请按照上述检查点进行检查。

10、HDMI部分电路i.MX 8MDQLQ提供了能够支持HDMI2.0兼容输出的HDMI发送器。

下图为HDMI部分线路连接图:

对于HDMI输出,每个高速输出对的正极和负极上的604电阻通过FET接地。 该FET的栅极应连接至HDMI传输电路(VDD_PHY_1V8)的1.8 V电源。 当HDMI传输电路断电时,这将自动断开电阻。 尽管单个FET足以实现功能,但每个信号的专用FET可以在信号之间提供更好的隔离,并使串扰最小化。这部分电路是为了更好的兼容HDMI2.0,用户需参考开发板设计,否则会出现兼容性问题。

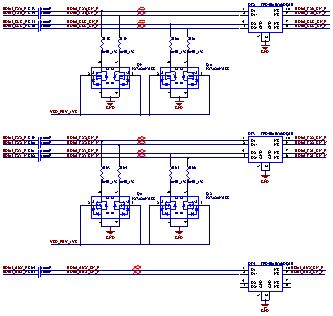

1、在进行PCB Layout时将604下拉电阻器直接放在信号线上,如下图所示:

2、差分线路阻抗控制位100ΩDifferential ±10%。

3、核心板上对数据线对间等长规则为≤100mil,建议底板保证同样的等长要求。

4、ESD器件靠近HDMI插座摆放。

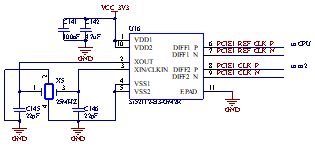

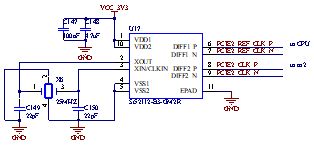

11、PCIE部分电路

MIMX8MQ6CVAHZAB芯片具有两个PCIE接口。每个都有一对名为PCIEx_REF_PAD_CLK_P / N的引脚。这些引脚用于从外部时钟源向PHY馈入100 MHz参考时钟。它们是仅输入引脚,不能输出时钟。请勿将它们连接到PCIE连接器或PCIE设备。

PCIE时钟产生器芯片(即Si52112)用于向PHY和连接器/设备提供高质量的时钟。如果没有PCIE时钟发生器,请使用芯片的内部时钟作为PHY的时钟源。内部时钟可以从CLK2_P / N(球T22和U22)输出,以向连接器/设备提供时钟。内部时钟的抖动比PCIE时钟发生器的抖动大。

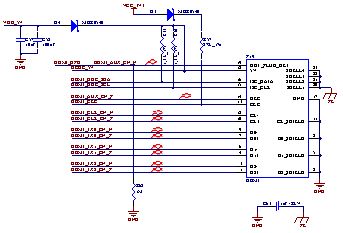

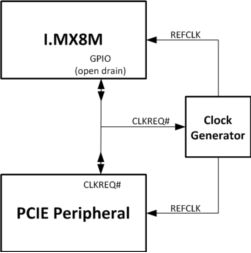

为了支持PCIE L1.1和L1.2 PM子状态,进入和退出这两种状态都需要一个双向漏极开路时钟请求(CLKREQ#)信号。这可以通过将GPIO(配置为漏极开路)直接连接到PCIE外设和时钟发生器的CLKREQ#信号来实现。下图为连接示意图:

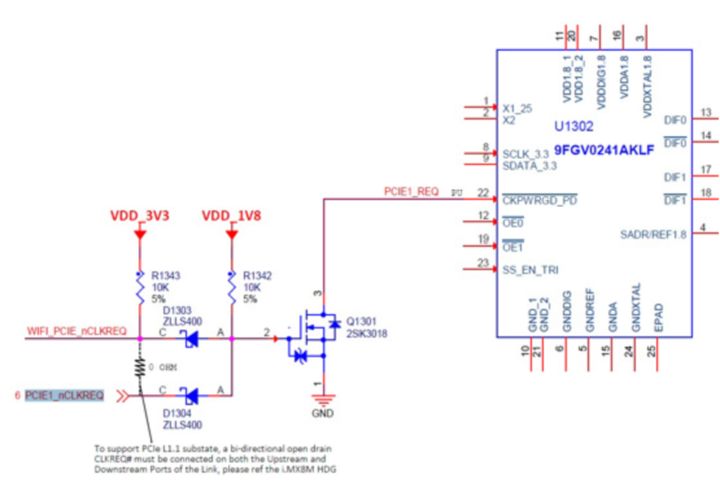

下图为参考原理图:

1、时钟线阻抗控制为100ΩDifferential ±10%,数据收发线阻抗控制为85ΩDifferential ±10%。

2、来自处理器的差分发射器必须是交流耦合的,在PCIE_TXP和PCIE_TXN输出上都使用0.1 F电容。

3、OKMX8MQ-C电路板设计使用器件Si52112。但是飞凌不推荐任何一家供应商,也不建议这是唯一的时钟发生器供应商,使用的设备应支持所有规格(抖动,精度等)。

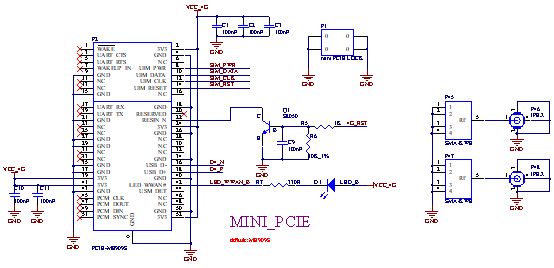

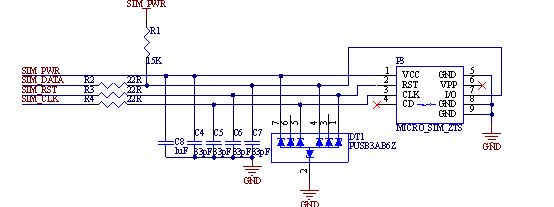

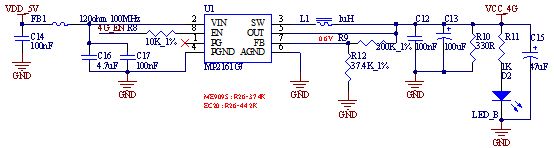

12、4G部分电路

开发板默认支持华为ME909S 4G模块,硬件设计请参考用户资料/硬件资料/数据手册中的《HUAWEI ME909s Series LTE Mini PCIe Module Hardware Guide-(V100R001_01, English)》。

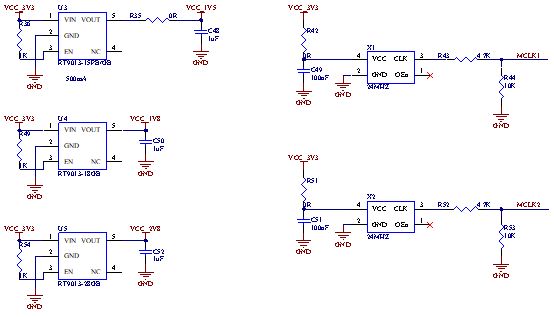

13、MIPI_DSI/CSI

1、 核心板没有输出1.5V、1.8V、2.8V电源,因此底板如果需要用到MIPI_CSI和MIPI_DSI功能时,需要用户自己设计LDO电路。

2、 核心板I2C接口为3.3V电平,因此需要做电平转换,可以参考开发板设计。

3、 MIPI_CSI和MIPI_DSI信号线在核心板分组等长,分为MIPI_CSI1、MIPI_CSI2、MIPI_DSI,组内等长规则为≤100mil,因此底板建议与核心板保持一致。

4、 数据线阻抗控制为100ΩDifferential。

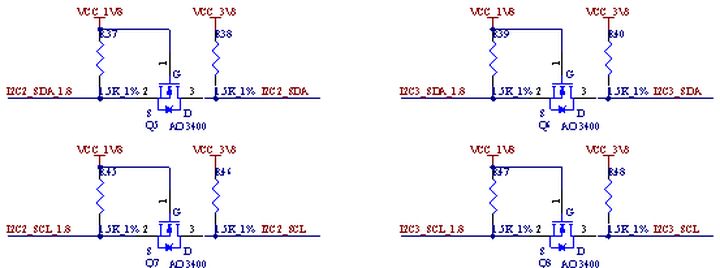

14、SPI转CAN部分电路

由于U13(MCP2551)供电电压为VDD_5V,U13端的IO高电平为5V,而U14端的IO高电平为3.3V,存在电平匹配问题。用户需要参考开发板设计,进行电平匹配。

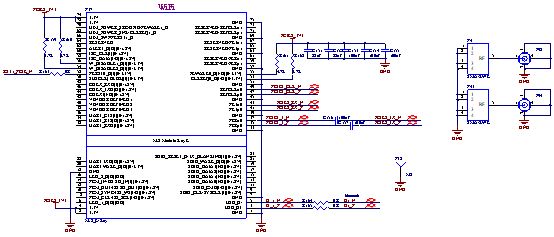

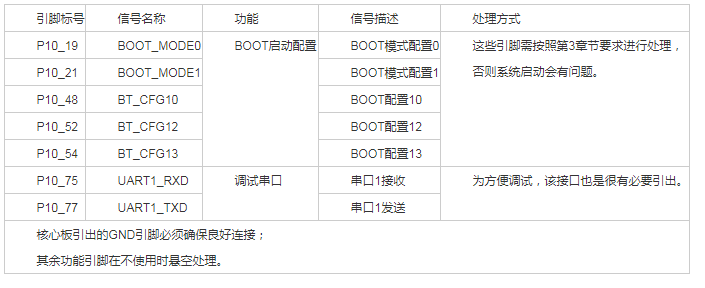

15、没有用到的引脚处理方式下表展示了FETMX8MQ-C核心板引脚处理方式:

连载:连载-iMX8MQ设计底板硬件指南-第一章

-

BMS中的继电器驱动电路总述2020-12-21

-

海芯中国区总部及集成电路研发生产基地停摆!2020-12-15

-

逆转衰老时钟!科学家成功恢复与年龄有关的视觉丧失!2020-12-03

-

夹具底板使用要点整理汇总2020-11-30

-

Nano Dimension:世界首块10层3D打印PCB电路板诞生2020-11-24

-

Vishay推出小型铝电容器,节省电路板空间2020-10-31

-

哈佛医学院用机器学习算法开发AI时钟,能够预测剩余寿命2020-09-22

-

“基因电路工”一兮生物:打开百亿级国产HMO市场2020-09-17

-

简化控制电路,这个无线充电方案让可穿戴设备远离充电烦恼2020-08-31

-

医疗器械设计:可伸缩柔性电路2020-04-17

-

AB1526对比CSR8670:通杀国内外TWS耳机电路方案,这两款蓝牙SoC究竟有何魔力?2020-01-08

-

从火爆的TWS耳机看中国集成电路的变化2019-11-09

-

西班牙科学家采用3D打印技术制高性能电路 可用于车辆等设备2019-11-03

-

60 V输入单芯片转换器可在没有超级电容或其他附加元件的情况下为关键电路供电2019-09-27

-

拨慢老去的时钟:最值得关注的10大长寿科技公司2019-09-09